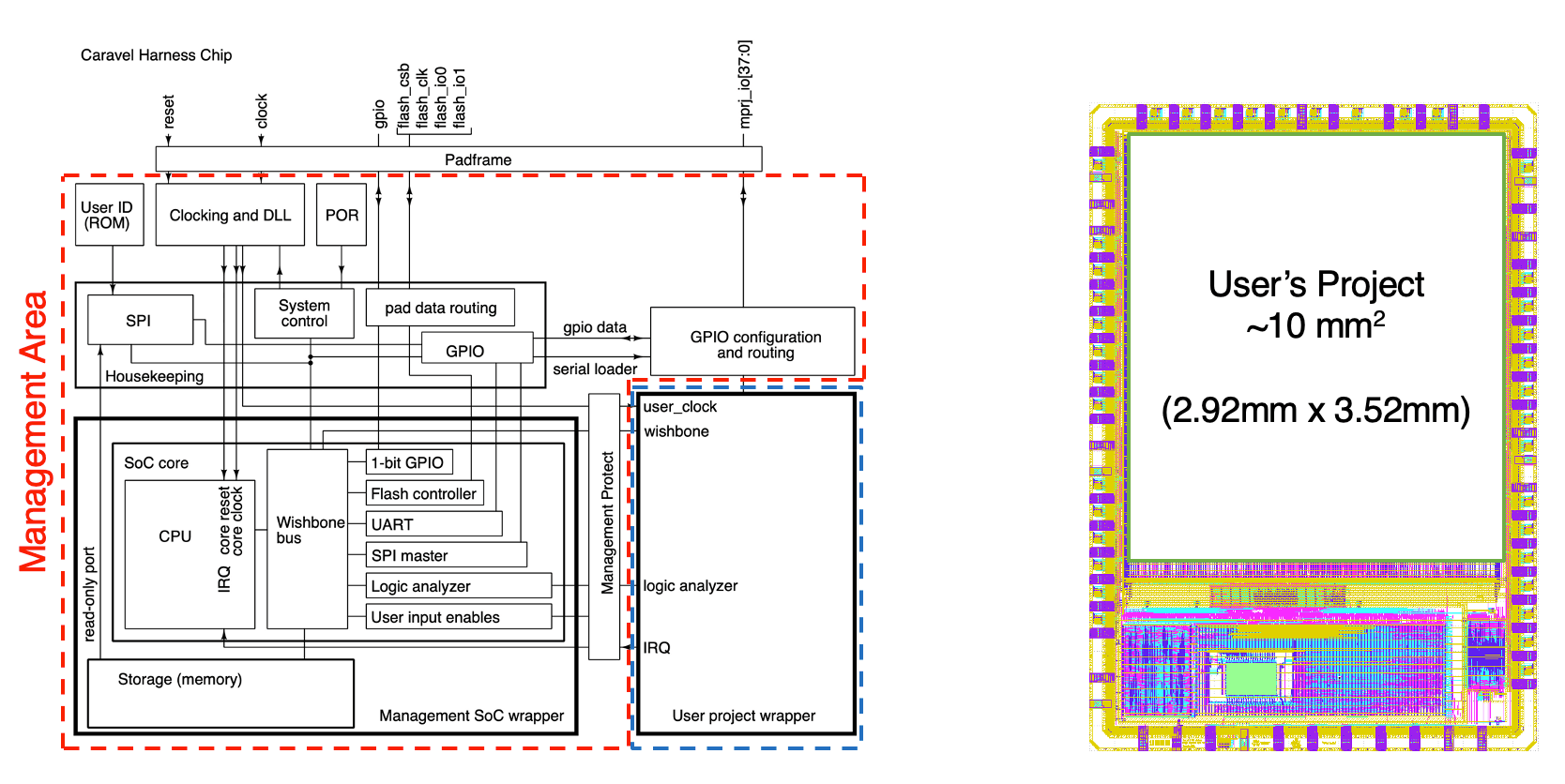

chipIgnite provides design and fabrication of a semi-custom ASIC incorporating your own design within a 10mm2 user area on the chip. The carrier chip provides all the infrastructure required for building a chip including IO and power, clock, reset, and a management SoC that can be used to drive your project.

The management SoC includes a RISC-V processor, SRAM and a wishbone bus that extends into the user area for connecting your own peripherals.

Features:

- 38 programmable IO's

- 10 mm2 of User Project Area

- Diagnostic port including IO configuration and Flash pass-thru access for programming

- VexRiscv CPU with debug

- 3 kbytes of RAM

- Flash controller supporting execute-in-place

- SPI, UART and GPIO

- Counter/Timers

- 128 signal logic analyzer for project

Find the documentation here

![[object Object]](https://static-files.umso.co/lib_CUsguFEVafmoKCKW/ns6hm1s6vu8ctynd.png?w=334)