Project Submission Requirements

The following project requirements must be met in order to qualify for inclusion on the shuttle program:

- The project must be targeted on the currently-supported SkyWater Open PDK for the 130nm process.

- The project must be posted on a git-compatible repo and be publicly accessible.

- The top-level of the project must include a LICENSE file for an approved open-source license agreement. Third-party source code must be identified and source code must contain proper headers. See details here.

- The repo must include project documentation and adhere to Google's inclusive language guidelines. See details here.

- The project must be fully open. The project must contain a GDSII layout, which must be reproducible from source contained in the project.

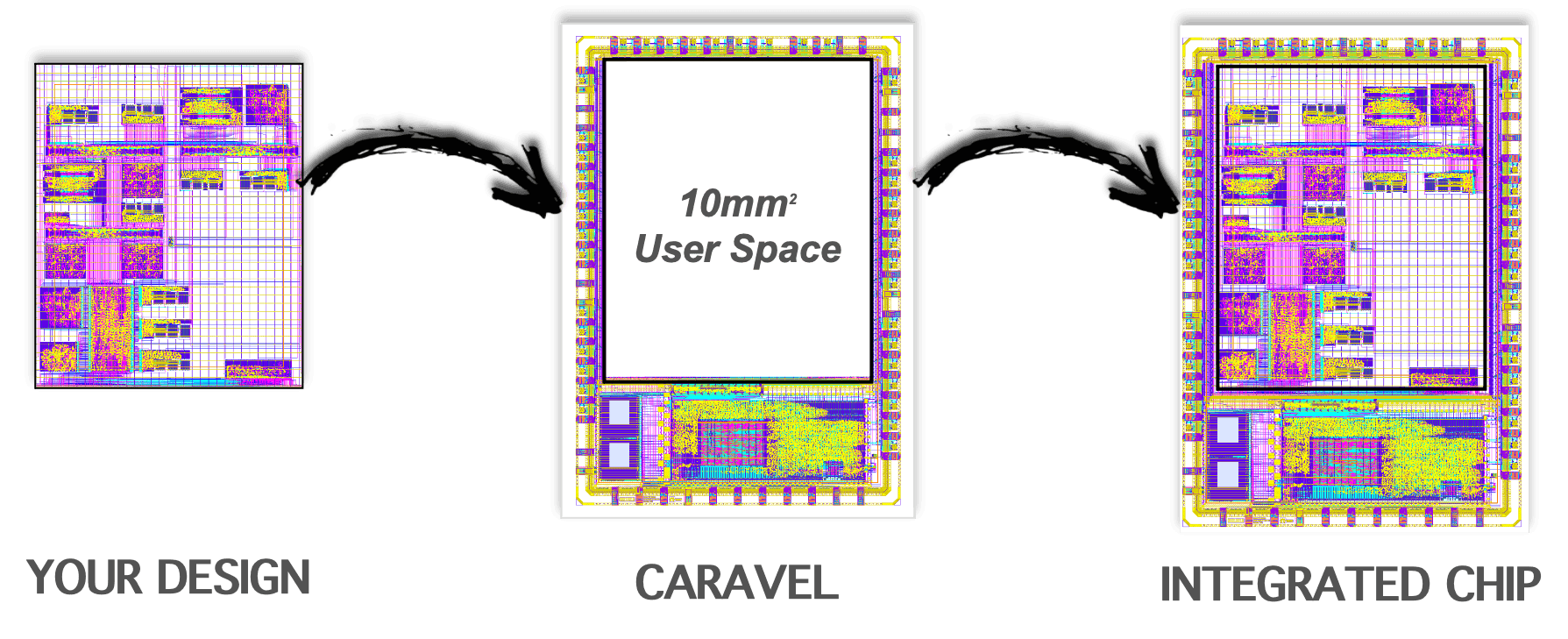

- Projects must use a common test harness and padframe based on the Caravel repo. New projects should start by duplicating or forking the Caravel User Project repo and implementing their project using the user_project_wrapper. The Caravel repo is configured as a submodule in the project under the ‘caravel’ directory. Note -- you do not need to initialize nor clone the Caravel sub-directory to complete or submit your project. See the project README for further instructions. The projects must be implemented within the user space of the layout and meet all requirements for the Caravel.

- Projects must successfully pass the Open MPW precheck tool, including LVS and DRC clean using the referenced versions of OpenLane flow. Projects should implement and pass a simulation test bench for their design integrated into Caravel. The Caravel User Project provides an example of how to implement this.

![[object Object]](https://static-files.umso.co/lib_CUsguFEVafmoKCKW/ns6hm1s6vu8ctynd.png?w=334)