Happy New Year to all,

2019 saw the emergence of “open” for semiconductor chips. In various ways, companies like Amazon, Google, IBM and many others expanded their efforts or joined the fray. For Efabless, “open” means chip design that is accessible to customers and innovators alike. This is a world where customers co-design ICs through rich interaction with a global community of companies, professionals and academics – creating the right solution for their particular needs. Efabless achieved important milestones in 2019 as we turned this vision into reality, including:

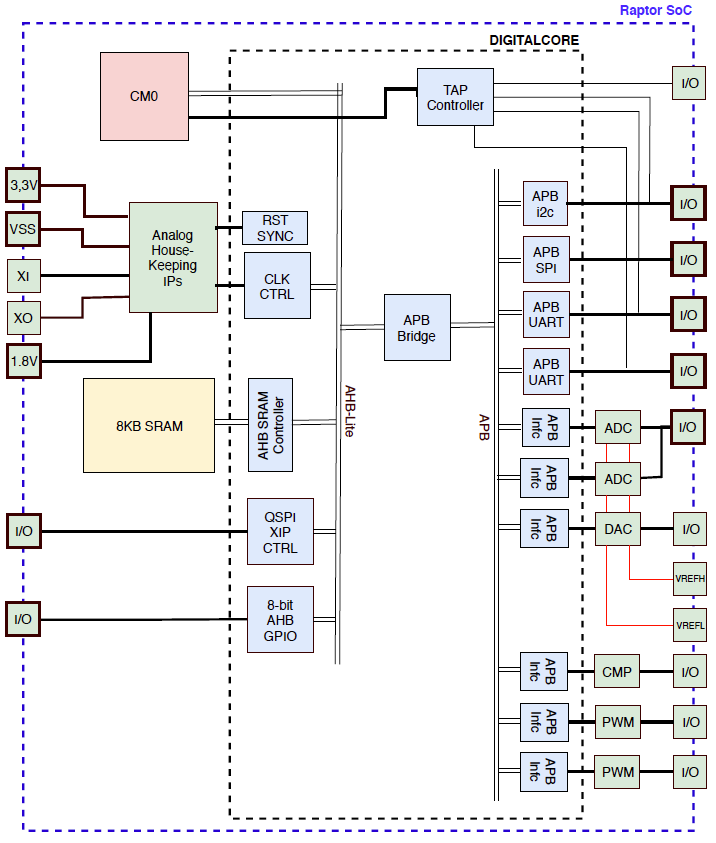

- Taped-out the Arm-based Raptor system development SoC, the first configurable open source template offering

- Engage our first customer to create a derivative of our community-developed RISC-V SoC, Raven

- Added support for GlobalFoundries 130G node to our platform and announced a program to enable associated design and IP development. This is in addition to the existing 180nm and 350nm nodes from XFAB.

- Engaged and trained design partners, including Sankalp, in utilizing the platform. Sankalp successfully completed multiple customer deliveries.

- Taped-out four successful community accessible SoCs. Each will be showcased as we move into 2020.

- Showcased the community-developed RISC-V SoC, Raven, in a chiplet-based “ZiP” solution for zGlue

- Expanded our customer and partner engagements to include Arm, AFRL, Google, NEC and GlobalFoundries among others.

This past year also saw our involvement in a design challenge with AFWERX (an AFRL- supported organization) for the U.S. Air Force, that provided a look into the true power of open innovation when applied to ICs. This open call for designs resulted in over 80 unique 14nm SoC designs for autonomous applications, ten of which have been selected to go through final design and ultimate demonstration in their intended applications.

In collaboration with Arm, we released our first open source design template, Raptor – based on the Arm M0. Templates are pre-engineered SoC designs that can be customized on our platform through a series of pull down menus, making ASIC design inexpensive, simple and fast. The open source template is a major development in simplifying custom SoC design, reducing the cost of design by as much as 90% and time to tape-out by 80%. And most importantly, we opened the definition of these templates enabling design firms and other community members to create derivative of existing templates and entirely new templates targeting different applications, foundry nodes and IP.

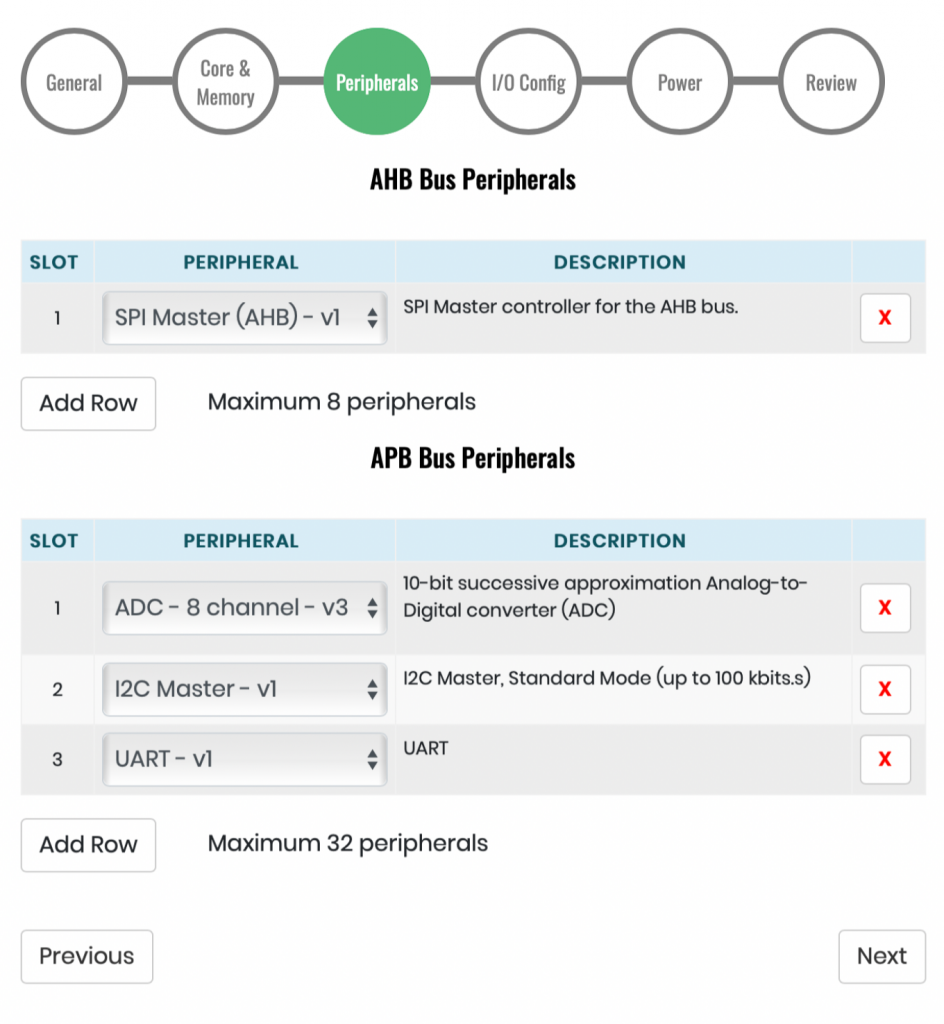

Design Configurator

We simplified interaction with SoC templates through a wizard-like interactive model using drop down menus to choose various IP and I/O configurations.

First Customer for Raven

First silicon arrived for our Raven RISC-V device and we engaged with our first customer derivative design – fully executing our community model. The complete design has been release on Github as an open source template.

RISC-V based ZiP by zGlue

We partnered with zGlue to offer our Raven on an interposer – our first move into multi-chip solutions

Customers and Partners

![[object Object]](https://umsousercontent.com/lib_CUsguFEVafmoKCKW/ns6hm1s6vu8ctynd.png?w=334)