We are now in an exciting time where the realization of custom SoCs is cost-effective and affordable for small companies or low-volume projects. Those unfamiliar with custom chip design may find it daunting to move away from the world of off-the-shelf components but the benefits abound and are well within reach. In this short article we’ll help you understand the benefits of creating a custom Arm-based SoC via Efabless SoC design templates and show you how the Efabless platform and community makes the process easy, fast and affordable.

If you have developed an electronic product using off-the-shelf components you are familiar with the numerous pain points encountered when moving from prototype through to distribution. The path of creating a custom SoC relieves many pain points along the way including:

- Controlling the most critical parts in your supply chain

- Simplifying part sourcing and reducing BOM complexity saving you money

- Reducing power consumption and product footprint giving you more room for the features that differentiate your product.

- Protecting your intellectual property and preserving your competitive advantage from copycats

The two most common misconceptions that cause companies to dismiss creating a custom SoC are cost and complexity. Arm, through its DesignStartTM program, is doing a great job of dispelling these misconceptions. They have helped numerous small companies reduce the challenges and licensing costs to develop Cortex M0 and M3 designs. DesignStart provides a great jump start in getting access to processor and subsystem IP needed for an SoC design. However, Efabless builds on and complements DesignStart by providing not only a complete set of analog and digital IP required for a full SoC implementation, but also tools and resources that help you every step of the way until you have a custom part in hand. Efabless provides options for you to develop the SoC yourself using tools and resources available through our platform, or through a turn-key design service that can provide samples in hand for as low as $70k.

Depending on the path you choose, the Efabless platform can help you with:

- Discovering and selecting vetted, reliable and proven IP

- Integrating off-the-shelf and your custom IP blocks into your design

- Online tools to simulate, validate, and synthesize your design

- Fabrication services with guidance through tape-out, production and packaging

Designing a custom SoC isn’t as expensive or complex as you think. The mature process technologies offered on the Efabless platform support mixed signal designs with low power utilization at a fraction of the cost. Open source and royalty free IP can be easily found in our marketplace, and our strong relationships with Arm and well-established foundries allow you to drop in an Arm Cortex processor, plug in analog and digital IP, fill in your product differentiating IP and have initial parts back from fab in as little as 20 weeks. Along with the low price tag, that is an 80-90% cost reduction and up to an 80% time reduction for a custom SoC.

Efabless design templates and open-source technologies are at the heart of this value offering. In contrast to the Arm DesignStart program, we’ll now show you how Efabless provides you an easier, faster, more affordable path to design shipment.

The Path to Custom Parts in Your Hand

The Efabless platform gives you options with respect to how you go from idea to parts in hand. One approach is to submit a request to the Efabless community for a custom SoC design and have experts do the ground work to get your design realized. Another approach is to leverage the Efabless online tools to handle some of the design process yourself and having Efabless pick up where you left off to finish things up. Both approaches start with the selection of a design template and Efabless has a number of templates to work with depending on your application needs.

The general process of going from idea to tape-out looks like this:

Select an SoC design template based on your application

- Configure the SoC using a library of pre-integrated IP

- Create a project based on the configuration and generate the top-level design

- Verify the base design through test benches and simulation

- Optional — Modify and re-verify the design to add custom logic, verification, etc.

- Optional — Prototype your solution using an evaluation board or FPGA

- Complete the physical design, tape-out, package and test

Efabless SoC templates exist for several platforms.

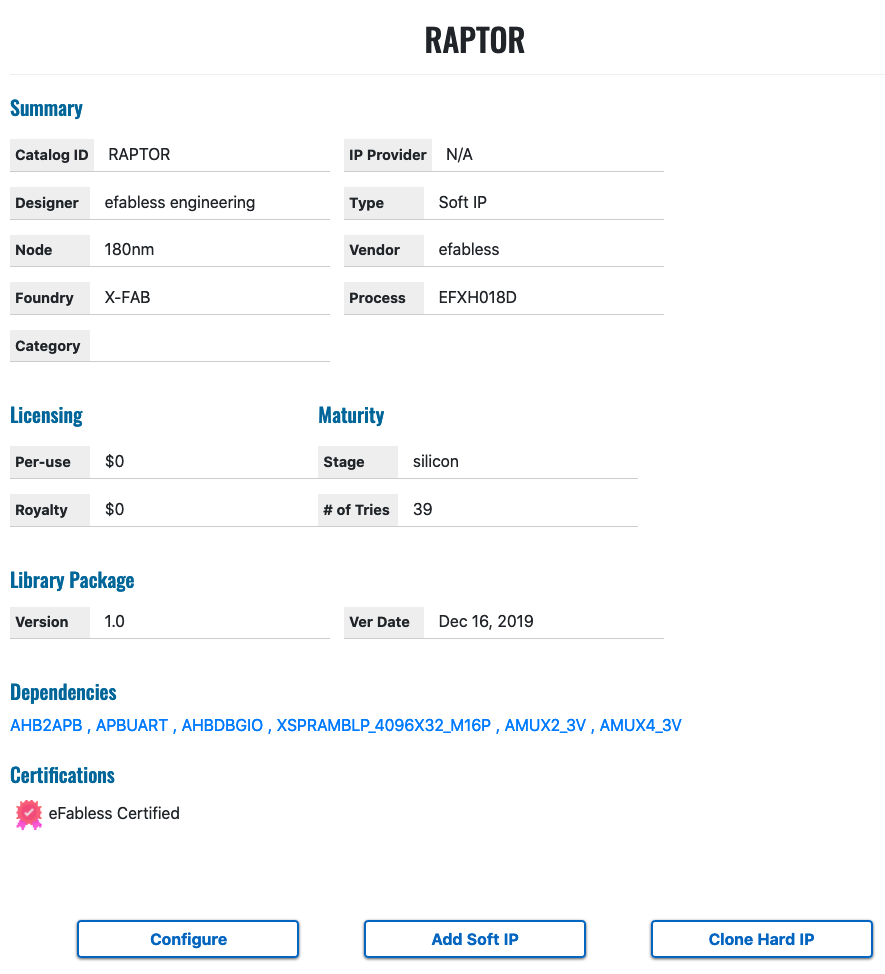

In the remainder of this article we’ll work with the Raptor template based on the Arm Cortex M0 processor and walk through the first two steps above. In future articles, we’ll address the remaining steps. Clicking on a template will give you more detailed information about the SoC such as its process technology, licensing fees, maturity details and any dependencies.

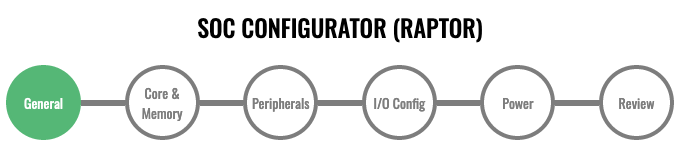

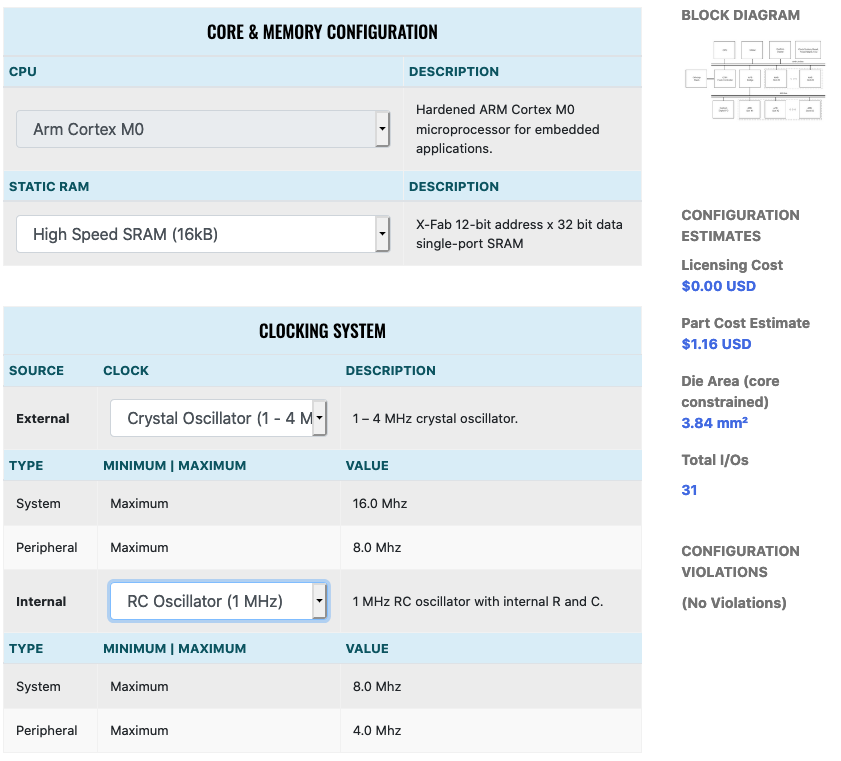

Clicking on the Configure button kicks-off the web-based configuration tool for the SoC template. The overall flow for that entails capturing some general information about your design, customizing your SoC core & memory, selecting peripherals from pre-integrated IP, configuring I/Os and the part’s package followed by configuring the system’s power settings.

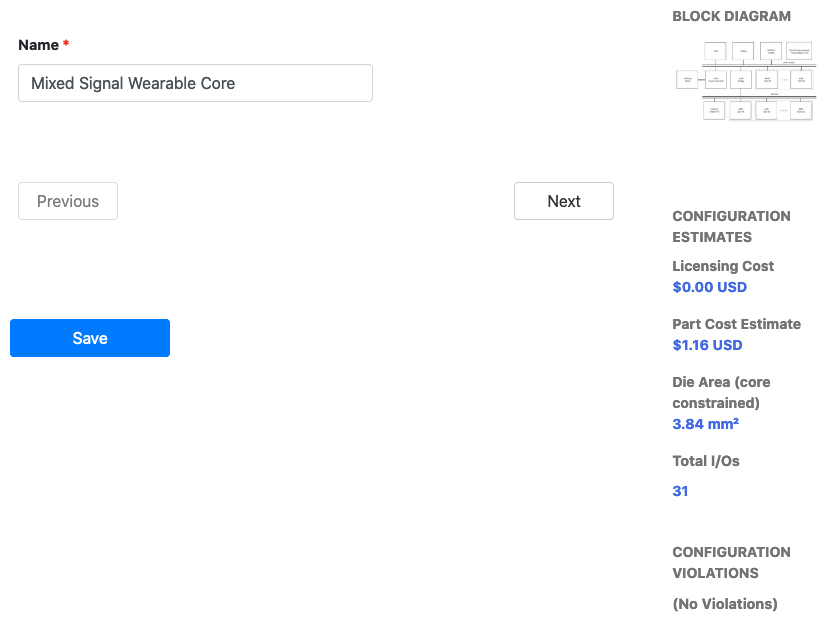

Right from the start, the design template shows you an estimate of the licensing cost, a per part cost estimate, the physical die size and the number of I/Os of your design. We’ll fill in the form as you see below and click Next.

This stage of the process shows you a block diagram of your design and though simple drop-down boxes lets you quickly select your SoCs CPU core, memory configuration and system clocking parameters. You’ll notice that as you make your choices, the panel showing the licensing, part cost and die area is automatically updated.

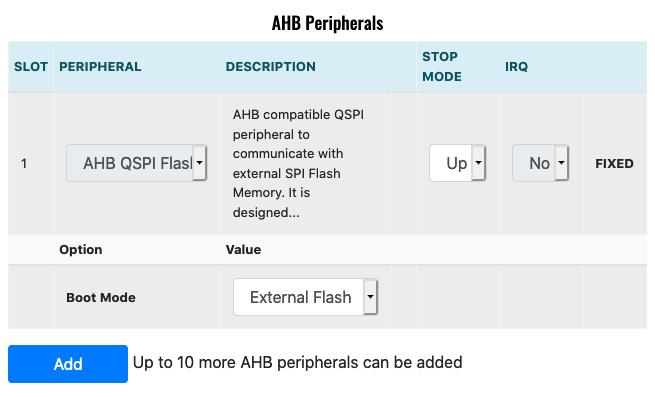

Next the template allows you to select your SoC’s peripherals from a list of pre-selected proven IP. On the System Bus (AHB) you can add up to 10 peripherals that will be tightly coupled with the CPU core.

On the Peripheral Bus (APB) you can add up to 15 general purpose peripherals such as timers, serial communication interfaces, comparators, analog to digital or digital to analog converters, etc.

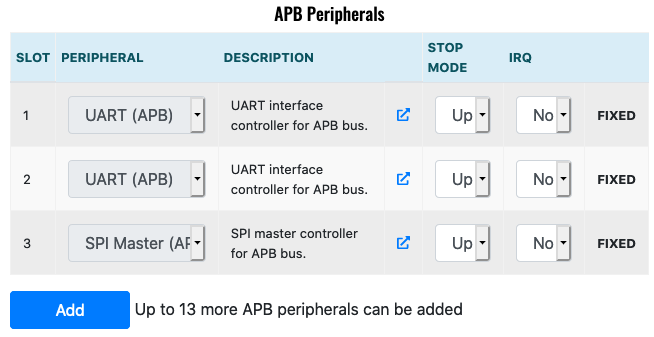

With the CPU, memory and peripherals selected, the next section provides you with the option to configure the I/Os of your system. Additionally, you can choose the package format that will satisfy the I/O and pin requirements of your system. The template will alert you to any specific configuration that needs to happen, such as selecting a package with enough pins to satisfy your design’s I/O requirement.

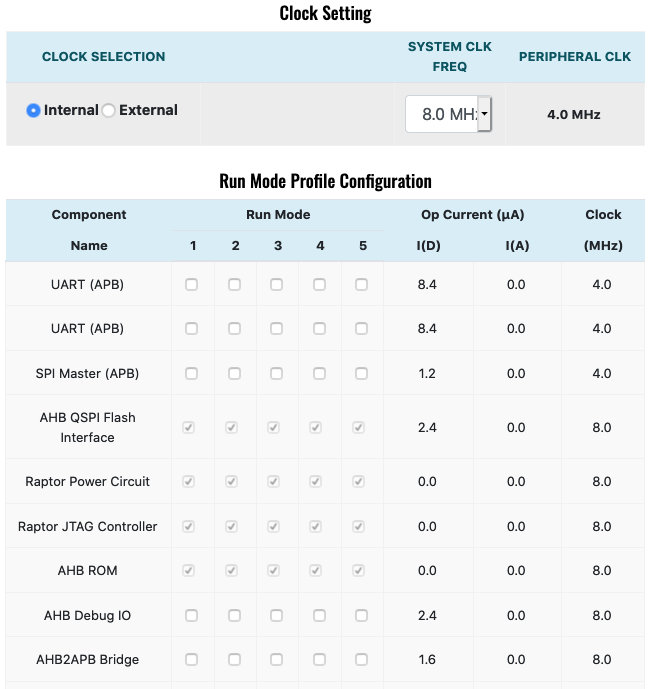

The next stage of the process presents you with a power estimation calculator. Start by selecting an operating frequency based on the source clock you chose previously. You can then configure each peripheral to be active or inactive in up to 5 run-modes. By specifying the percentage of time you expect your application to operate in each mode, you can get a weighted average estimate of overall power consumption. From here, you can go back and explore various options or peripherals, memory or clock speeds to find an optimal configuration.

Upon completing these steps, you are presented with a summary of your choices. If you are happy with how things look, save your configuration and continue with the next part of the process. If you are new to the Efabless platform, you will need to register in order to save your configuration and proceed further. For the next steps, you have the following choices:

- Submit the SoC configuration to the Efabless community for completion

- Create a project where you will automatically generate a design based on your configuration and complete using the design flow available through the Efabless platform.

Summary

Designing a custom SoC for your application is easier and cheaper than ever before. The benefits of SoC creation for companies of all sizes, even those with low volumes, abound and the common misconceptions around the process can be quickly dismissed. Arm and the DesignStart program reduces the difficulty and cost to design using Arm Cortex M0 and M3 processors although there is quite some legwork that must be done to arrive at a physical part. The Efabless platform of tools and community of experts provide a comprehensive solution for custom SoC creation that is easy, fast and affordable. Through the use of Efabless design templates, companies can either submit requests for a turn-key service to realize a custom part for as little as $70k, or complete the design themselves leveraging design tools and fabrication services available through the platform. In follow-on articles we’ll pick up where we left off here and show you how the Efabless design flow will allow you to create a project based on your SoC configuration. For now, check out the Efabless Arm Cortex-M0 SoC design template.

Part 2: Efabless & Arm Enable Fast Affordable Custom SoC Development

![[object Object]](https://umsousercontent.com/lib_CUsguFEVafmoKCKW/ns6hm1s6vu8ctynd.png?w=334)